台积电日前宣布,已经开始了7nm+ EUV工艺的大规模量产,这是该公司乃至整个半导体产业首个商用EUV极紫外光刻技术的工艺。作为EUV设备唯一提供商,市场预估荷兰ASML公司籍此EUV设备年增长率将超过66%。这个目标是否能实现?EUV工艺在发展过程中面临哪些挑战?产业化进程中需要突破哪些瓶颈?

EUV设备让摩尔定律再延伸三代工艺

光刻是集成电路生产过程中最复杂、难度最大也是最为关键的工艺,它对芯片的工艺制程起着决定性作用。193nm浸没式光刻技术自2004年年底由台积电和IBM公司应用以来,从90nm节点一直延伸到10nm节点,经历了12年时间,是目前主流的光刻工艺。但是进入7nm工艺后,它的制约也越来越明显,因此EUV工艺堂而皇之走上舞台。

全球EUV光刻技术的研发始于20世纪80年代,经过近40年的发展,EUV技术从原理到零部件再到原材料等已经足够成熟,并且在现阶段的产业应用中体现了较明显优势。

研究院王珺在接受《中国电子报》记者采访时表示,极紫外光(EUV)短于深紫外光(DUV)的波长,这让EUV光刻技术的应用显著提升了光刻机曝光分辨率,进而带动晶体管特征尺寸的缩减。制造企业在28nm及以下工艺的解决方案使用浸没式和多重曝光技术。但是进入7nm工艺,DUV的多重曝光次数增长太多,让制造成本、难度、良率、交付期限均显著恶化。在关键层应用EUV光刻技术,从而减少曝光次数,进而带来制造成本与难度的降低,这让EUV光刻技术具备了足够的生产价值。

“EUV光刻机在5nm及以下工艺具有不可替代性,在将来较长时间内应用EUV技术都将成为实现摩尔定律发展的重要方向。”王珺说。因此,从工艺技术和制造成本综合因素考量,EUV设备被普遍认为是7nm以下工艺节点最佳选择,它可以继续往下延伸三代工艺,让摩尔定律再至少延长10年时间。

DRAM存储器将带动EUV光刻机增长

在台积电、三星、英特尔继续延续摩尔定律进行工艺发展的带动下,EUV光刻机的应用数量将持续提升。

王珺表示,从目前看,对EUV光刻技术具有明显应用需求的芯片包含应用处理器、CPU、DRAM存储器、基带芯片。

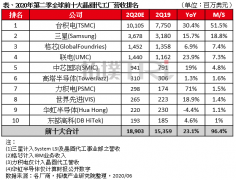

半导体专家莫大康认为,ASML公司EUV设备产量若要进一步扩大,希望就落在存储器厂商身上。他向《中国电子报》记者表示,目前看,EUV光刻机主要卖给三家公司:英特尔、三星和台积电,其中台积电订得最多。他介绍说,存储器主要分为两种:一种是DRAM,另一种是3D NAND。3D NAND目前的竞争主要集中在层数上,虽然也需要工艺的先进性,但需求不那么迫切。而DRAM存储器则不同,一方面其产量比较大,另一方面若做到1Z(12~14nm)以下,就可能需要用到EUV光刻机了,届时,存储器厂商订的EUV设备将有大的爆发。“但具体时间,还要看市场需求以及厂商导入情况。目前,ASML公司EUV设备一年的出货量只有40多台,远远未达到业界预期。”

EUV还需克服诸多挑战

现阶段EUV光刻技术已经成熟,且进入产业化阶段,但是在光刻机的光源效率、光刻胶的灵敏度等方面依然存在较大的进步空间。

有关人士指出,EUV光刻机除了价格昂贵之外(超过1亿美元),最大的问题是电能消耗,电能利用率低,是传统193nm光刻机的10倍,因为极紫外光的波长仅有 13.5nm,投射到晶圆表面曝光的强度只有光进入EUV设备光路系统前的2%。在7nm成本比较中,7nm的EUV生产效率在80片/小时的耗电成本是14nm的传统光刻生产效率在240片/小时耗电成本的1倍,这还不算设备购置成本和掩膜版设计制造成本比较。

莫大康认为EUV工艺面临三大挑战:首先是光源效率,即每小时刻多少片,按照工艺要求,要达到每小时250片,而现在EUV光源效率达不到这个标准,因此还需进一步提高,且技术难度相当大。其次是光刻胶,光刻胶的问题主要体现在:EUV光刻机和普通光刻机原理不同,普通光刻机采用投影进行光刻,而EUV光刻机则利用反射光,要通过反光镜,因此,光子和光刻胶的化学反应变得不可控,有时候会出差错,这也是迫切需要解决的难题。最后是光刻机保护层的透光材料,因为光刻机精度越来越高,上面需要一层保护层,现在的材料还不够好,透光率比较差。

在以上三个挑战中,光源效率是最主要的。此外,EUV光刻工艺的良率也是阻碍其发展的“绊脚石”。目前,采用一般光刻机生产的良率在95%,EUV光刻机的良率则比它低不少,在70%~80%之间。莫大康表示,解决上述问题,关键是订单数量,只有订单多了,厂商用的多了,才能吸引更多光源、材料等上下游企业共同参与,完善EUV产业链的发展。

王珺表示,EUV技术的研发与应用难度极高,将来实现进一步发展在全球范围内将遵循竞争优势理论,各国和地区的供应商依靠自身优势进行国际化产业整合。